-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

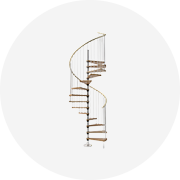

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

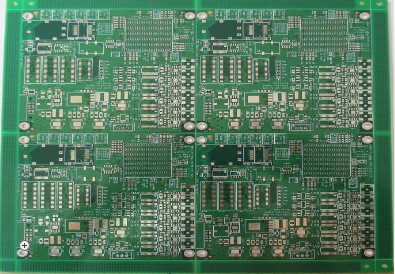

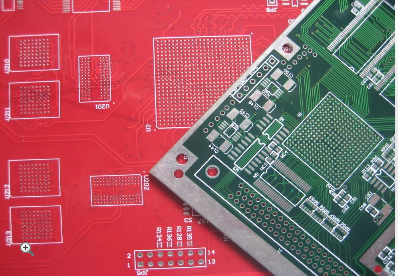

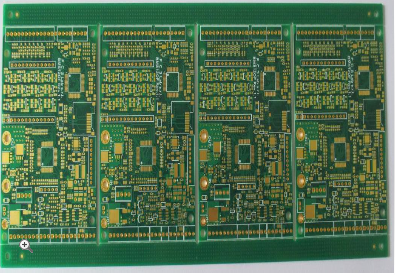

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

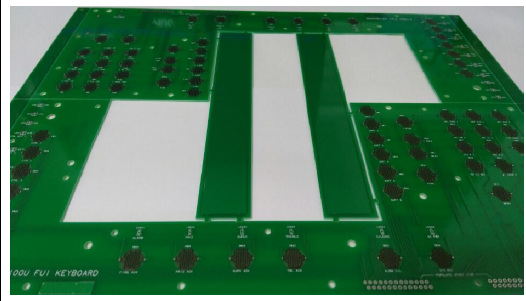

Innovative Multilayer PCB Fabrication Techniques For Scalable Server Motherboards Supporting AI Workloads

The relentless expansion of artificial intelligence is fundamentally reshaping the computational landscape, placing unprecedented demands on the hardware that powers it. At the heart of every AI server lies the motherboard, a complex nexus where processing units, memory, and interconnects converge. However, traditional printed circuit board (PCB) fabrication methods are increasingly proving inadequate for the high-speed, high-power, and thermally intensive requirements of modern AI workloads. To support the scalable, efficient, and reliable servers needed for tomorrow's AI breakthroughs, a new generation of innovative multilayer PCB fabrication techniques is emerging. These advancements are not merely incremental improvements; they represent a paradigm shift in how we design and manufacture the foundational platform for computational intelligence, enabling the dense integration and lightning-fast communication essential for training large language models and executing complex inferencing tasks.

Advanced Lamination Processes for Enhanced Layer Count and Integrity

As server motherboards for AI applications incorporate more layers—often exceeding 20 or even 30—to accommodate intricate power delivery networks and dense signal routing, conventional lamination processes face significant challenges. The primary issue is the increased risk of delamination, warping, and voids when bonding such a high number of layers under heat and pressure. Innovative techniques are addressing this by utilizing low-loss, high-glass-transition-temperature (Tg) laminates that offer superior dimensional stability and can withstand multiple lamination cycles.

Furthermore, sequential lamination has become a critical strategy. Instead of laminating all layers at once, the board is built up in smaller, manageable sub-assemblies. For instance, the core complex with the CPU and its immediate memory interfaces might be laminated first, followed by the addition of peripheral and power layers. This approach minimizes stress on the entire structure, reduces the risk of defects, and allows for more precise control over the dielectric thickness between critical signal layers. It also enables the incorporation of different material types within the same board, optimizing performance for specific sections, such as using materials with a lower dielectric constant (Dk) for high-speed channels and materials with better thermal conductivity for power sections.

High-Density Interconnect (HDI) and Microvia Technology

The immense data throughput required by AI processors, such as GPUs and TPUs, necessitates an extremely high density of interconnections on the motherboard. Standard through-hole vias are too large and consume valuable real estate that could be used for component placement or additional routing. This is where High-Density Interconnect (HDI) technology, particularly the use of microvias, becomes indispensable. Microvias are laser-drilled holes with diameters typically less than 150 microns, allowing for direct connections between adjacent layers.

Advanced fabrication employs stacked and staggered microvia structures to create vertical pathways through multiple layers without the need for a large, mechanically drilled via that passes through the entire board. This frees up significant routing channels on the inner layers, enabling more efficient escape routing from high-pin-count BGA packages. The use of any-layer HDI, where microvias can be placed on any layer of the PCB, provides ultimate design flexibility. This technology is crucial for managing the fan-out of thousands of connections from modern AI accelerators, ensuring signal integrity is maintained by minimizing stub lengths and providing a cleaner return path for high-frequency signals, which is paramount for achieving the multi-gigabit per second data rates demanded by AI workloads.

Precision Materials for Signal and Power Integrity

The performance of an AI server motherboard is critically dependent on the electrical properties of the PCB materials. At the high frequencies involved, signal loss becomes a major concern. Standard FR-4 material exhibits significant dielectric loss (Df), which attenuates signals and degrades their quality. To combat this, innovative fabrication relies on specialized low-loss laminates, such as those based on polyphenylene ether (PPO) or hydrocarbon ceramics. These materials have a much lower dissipation factor, preserving signal strength and integrity over longer traces on the motherboard.

Equally important is power integrity. AI processors can draw hundreds of amps with rapid current transients. The PCB's power distribution network (PDN) must deliver this power with minimal voltage fluctuation. This requires a low impedance path from the voltage regulator modules (VRMs) to the processor. Fabrication techniques now incorporate a greater number of dedicated power and ground planes, often using thicker copper (e.g., 2oz or 3oz) to reduce DC resistance. The use of low-inductance decoupling capacitors placed in close proximity to the processor, facilitated by HDI technology, is also a key part of the material and layout strategy. The selection of materials with a stable dielectric constant across a wide frequency range is also essential to maintain consistent impedance control for high-speed signals, preventing reflections and ensuring data transmission accuracy.

Thermal Management Integration within the PCB Structure

The immense computational power of AI servers generates substantial heat, which, if not managed effectively, can lead to thermal throttling and reduced reliability. While heatsinks and fans are external solutions, innovative PCB fabrication integrates thermal management directly into the board's structure. A primary method is the incorporation of metal cores, typically aluminum or copper, within the PCB stack-up. These insulated metal substrates (IMS) provide a highly efficient path for heat to be drawn away from high-power components like GPUs and dissipated over a larger area.

For even more demanding applications, embedded copper coins or thermal bars are used. These are solid blocks of copper that are pre-machined and embedded into the PCB substrate directly beneath a specific hot component. They offer superior thermal conductivity compared to a full metal core, providing a targeted cooling solution. Another advanced technique involves the use of thermal vias—arrays of small, copper-plated holes filled with thermally conductive epoxy—underneath component packages. These vias transfer heat from the top-side components down to internal ground planes or to a heatsink on the bottom side of the board. By managing heat at the source within the PCB itself, these techniques enable higher sustained performance and improve the long-term longevity of the server motherboard.

Automated Optical Inspection and Testing for Uncompromising Quality

The complexity and density of scalable AI server motherboards make manual inspection impractical and unreliable. Therefore, the fabrication process is heavily reliant on advanced Automated Optical Inspection (AOI) systems. These high-resolution cameras scan the PCB layers before and after lamination to detect minute defects such as opens, shorts, nicks, or debris that could compromise functionality. For the dense patterns and microvias, AOI is essential for ensuring manufacturing yield.

Beyond visual inspection, electrical testing is paramount. Flying probe testers and dedicated fixture testers verify the electrical connectivity of every net on the board, ensuring there are no open or short circuits. For high-speed designs, more sophisticated testing like Time Domain Reflectometry (TDR) is employed to characterize impedance profiles of critical traces and verify that they meet the strict design specifications. These rigorous quality control measures, integrated throughout the fabrication process, are non-negotiable for producing server motherboards that can reliably operate in data center environments, where any failure can result in significant downtime and cost.

REPORT