-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

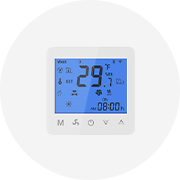

- Floor Heating Systems & Parts

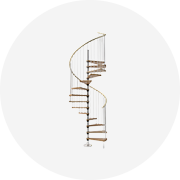

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

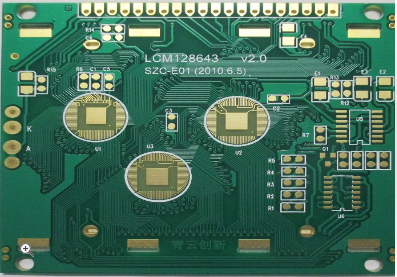

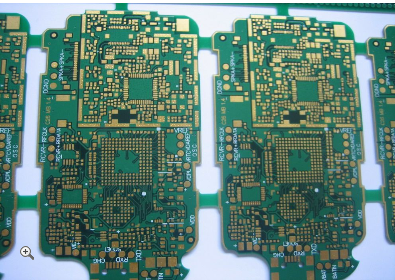

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

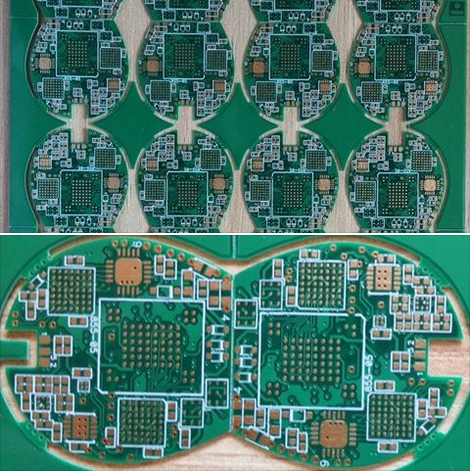

Optimized Plating Half Holes PCB Processes For Maximum Conductivity And Long Term Operational Efficiency

In the intricate world of printed circuit board (PCB) manufacturing, the pursuit of perfection is relentless. Among the many specialized techniques employed, the creation and plating of half-holes, or castellated holes, stands out as a critical process for enabling board-to-board connections, module stacking, and edge-board mounting. These plated semi-circular notches along the board edge are not merely aesthetic features; they are fundamental conduits for electrical and mechanical integrity. The article "Optimized Plating Half Holes PCB Processes For Maximum Conductivity And Long Term Operational Efficiency" delves into the sophisticated engineering behind transforming these vulnerable board edges into robust, high-performance interconnects. As electronic devices shrink in size but grow in complexity and power demands—from advanced IoT modules and RF devices to compact wearable technology—the reliability of every connection point becomes paramount. This discussion is not just for PCB engineers; it is crucial for product designers, quality assurance specialists, and procurement managers who understand that the longevity and performance of an entire electronic system can hinge on the microscopic quality of a plated half-hole. By exploring optimized processes, we uncover how modern manufacturing transcends basic functionality to achieve maximum conductivity and ensure operational efficiency that endures through thermal cycles, mechanical stress, and the test of time.

Precision Drilling and Routing: The Foundation of Integrity

The journey to an optimized plated half-hole begins long before any metal is deposited; it starts with the creation of the hole itself. The initial drilling and routing phase sets the geometric and surface-quality precedent for all subsequent steps. Traditional drilling methods can leave behind micro-fractures, burrs, or uneven surfaces at the rim of the half-hole, which become weak points that compromise plating adhesion and ultimately, electrical continuity. Optimized processes employ high-precision, numerically controlled (CNC) routing with specialized carbide bits designed for clean, shear-cutting of the laminate and copper. The parameters—such as spindle speed, feed rate, and tool path—are meticulously calibrated based on the specific PCB material (e.g., FR-4, high-Tg, or Rogers substrates) to achieve a smooth, uniform cavity wall.

Furthermore, the sequence of operations is critical. An optimized protocol often involves drilling a complete through-hole first, followed by a precise routing operation to slice it in half, rather than attempting to route a semi-circle directly. This method provides better support for the material during cutting, reducing chipping and delamination at the critical edge where the plating will terminate. The cleanliness of this stage cannot be overstated; any residual debris or roughness creates nucleation sites for uneven plating, leading to potential voids or thin spots. Therefore, integrated vacuum systems and post-machining cleaning, such as plasma treatment or specialized chemical desmear, are employed to ensure a pristine, activation-ready surface. This foundational attention to detail ensures the half-hole is a perfect receptacle for the conductive layers to follow, directly influencing the final current-carrying capacity and mechanical bond strength.

Advanced Metallization and Plating Techniques

Once a perfect cavity is prepared, the core of the optimization process lies in the metallization. The goal is to build a conductive barrel within the half-hole that is uniform, pore-free, and possesses excellent adhesion to the substrate. The standard process involves electrodes copper deposition followed by electrolytic copper plating, but optimization demands far greater nuance. The initial electrodes copper bath, which provides the foundational conductive layer, must be carefully controlled for temperature, chemical concentration, and agitation to ensure a consistent deposit even on the vertical walls and the challenging curved surface of the half-hole's interior. Advanced catalytic systems are used to promote uniform nucleation, preventing the "skip-plating" or voids that are common failure points in non-optimized processes.

The subsequent electrolytic copper plating is where thickness, grain structure, and purity are engineered for performance. Optimized processes move beyond simple thickness specifications (typically 25-35 μm for robust half-holes). They focus on the morphology of the deposited copper. Using pulse or periodic reverse pulse plating techniques allows for superior control over grain size and distribution. Fine-grained, dense copper deposits exhibit lower electrical resistivity and higher resistance to fatigue cracking under thermal stress compared to coarse-grained, columnar structures. Additionally, the plating chemistry is formulated with high-purity additives and levelers to ensure the plating thickness is even from the top of the hole rim, down the wall, and across the curved bottom, eliminating weak thin areas. For applications requiring superior solderability or environmental resistance, a final finish—such as Electroless Nickel Immersion Gold (ENIG), Immersion Silver, or Selective Hard Gold—is applied with similar precision. This multi-layered, carefully controlled metallurgical approach is what transforms a simple hole into a high-conductivity, durable interconnect.

Rigorous Quality Control and Reliability Testing

Optimization is meaningless without verification. A hallmark of a superior half-hole plating process is an embedded, multi-stage quality control regimen. This begins with in-process monitoring. Automated optical inspection (AOI) systems equipped with high-magnification cameras and specialized lighting are used to inspect every half-hole for visual defects like nicks, plating folds, or exposed substrate immediately after plating and again after final finish application. Cross-sectional analysis, or microsectioning, remains the gold standard for quantitative assessment. Samples are periodically sacrificed, polished, and examined under a microscope to measure plating thickness at multiple points (top, middle, bottom of the hole wall), check for voids or cracks, and evaluate the intermetallic bond between layers.

Beyond dimensional checks, reliability testing simulates the harsh conditions of real-world operation. Thermal stress testing, such as Thermal Cycling (e.g., -55°C to +125°C) and Highly Accelerated Stress Testing (HAST), subjects the plated half-holes to repeated expansion and contraction. Optimized processes produce platings that survive these tests without developing cracks that would increase resistance or cause open circuits. Solderability tests, like wetting balance analysis, ensure the final finish promotes reliable solder joint formation during assembly. Furthermore, mechanical tests, including shear and pull strength tests on soldered connections, validate that the plating adhesion to the PCB substrate can withstand assembly and operational stresses. This data-driven feedback loop is essential; it not only catches defects but also informs continuous refinement of the drilling, cleaning, and plating parameters, closing the optimization cycle and guaranteeing long-term operational efficiency.

Design for Manufacturing (DFM) Collaboration

True optimization extends beyond the factory floor and into the design phase. The most advanced plating processes can be undermined by a PCB layout that does not consider the manufacturability of half-holes. Therefore, an optimized approach necessitates early and collaborative Design for Manufacturing (DFM) engagement between the PCB designer and the fabrication engineer. Key guidelines must be integrated into the design: specifying adequate annular ring size around the half-hole to prevent copper tearing during routing, defining optimal half-hole diameters and pitches for the chosen plating method, and indicating the required plating thickness and finish on the technical drawings. The board edge clearance and the positioning of other features relative to the half-holes are also critical to allow proper tool access and prevent damage.

This collaboration also involves material selection. The choice of core laminate, prepreg, and copper foil type influences the drilling quality and the thermal expansion coefficient (CTE). A significant CTE mismatch between the substrate and the copper plating can induce stress during temperature swings, leading to interfacial failures. An optimized process includes advising designers on material stacks that promote harmony with the plated copper. By embedding manufacturability rules into the design stage, the process sets the stage for success, reducing the risk of yield loss, preventing latent reliability issues, and ensuring that the designed half-holes are perfectly poised to achieve the maximum conductivity and longevity that the optimized plating process can deliver. This synergy between design intent and manufacturing capability is the ultimate safeguard for long-term operational efficiency.

REPORT